Top Tips for Advanced Semiconductor Packaging Substrate Design

You need to prioritize material selection for thermal and mechanical stability in every semiconductor packaging substrate project. Materials with high adhesion and robust thermal properties help you achieve reliable performance. Recent industry reports highlight how emerging technologies in semiconductor packaging enhance device integration and system-level performance. For example, stacking high bandwidth memory close to GPUs reduces latency and power consumption. The table below shows how next generation IC packaging drives advances in complexity, bandwidth, and integration.

| Aspect | Impact on Device Performance and Integration |

|---|---|

| Complexity of AI Chips | AI chips now contain up to a trillion transistors per package, requiring advanced packaging for system-level compute and memory integration. |

| High Bandwidth Memory (HBM) | Stacking memory vertically and placing it close to the GPU reduces latency, boosts data transfer speeds, and lowers power consumption. |

| Packaging Technologies | Hybrid bonding and 3D packaging architectures increase interconnect density, improve system performance, and reduce power loss, critical for AI workloads. |

| Future of Semiconductors | Advanced packaging meets next-generation semiconductor device requirements, emphasizing smarter integration over smaller transistors. |

Key Takeaways

- Choose materials wisely. Select substrates with high thermal and mechanical stability to ensure reliable performance.

- Implement effective thermal management. Use advanced cooling solutions and validate designs with simulation tools to maintain optimal device temperatures.

- Prioritize signal integrity. Use proper routing techniques and shielding methods to minimize crosstalk and enhance device performance.

- Collaborate with suppliers early. Engage with material and technology partners to improve design efficiency and reduce costs.

- Stay updated on industry standards. Following regulations ensures product safety and enhances market competitiveness.

Key Tips for Semiconductor Packaging Substrate Design

Material Selection Essentials

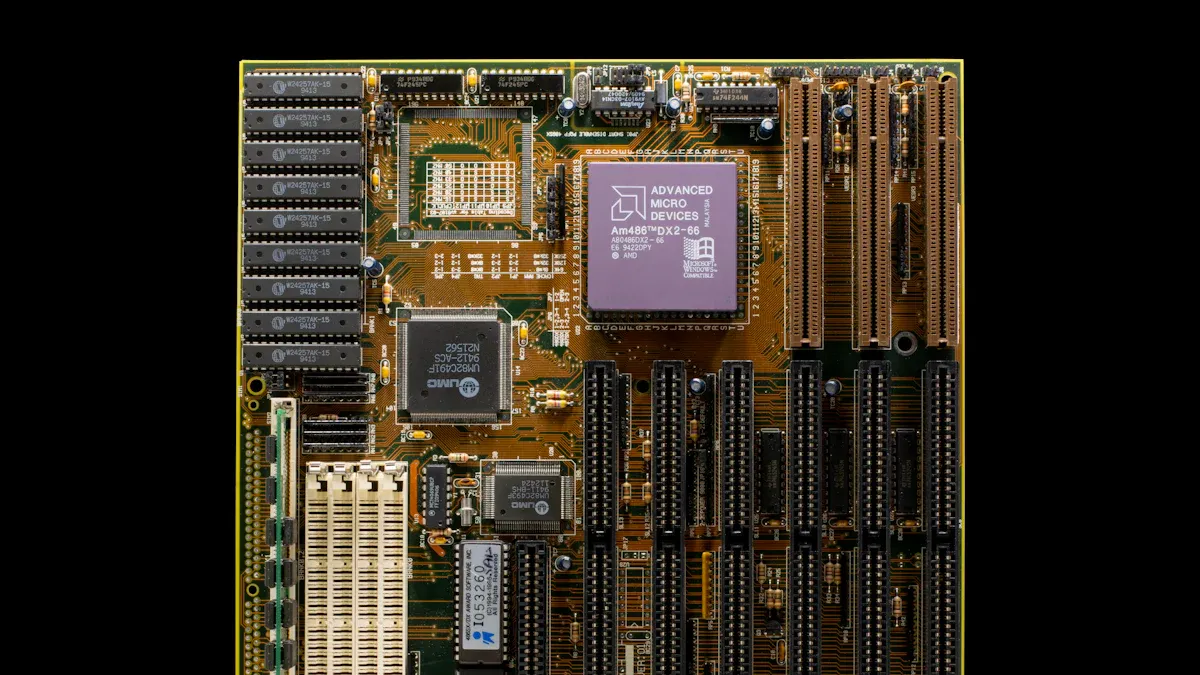

You need to select the right materials for your semiconductor packaging substrate to ensure reliable performance and long-term durability. The choice of substrate material directly affects thermal resistance, mechanical stability, and overall device reliability. Many engineers use FR-4 for cost-effective designs, but high-performance applications often require BT resin, ceramic, or polyimide. Each material offers unique advantages for advanced ic packaging design.

| Material | Thermal Properties | Mechanical Properties | Advantages |

|---|---|---|---|

| FR-4 | Adequate thermal resistance (up to 130°C) | Robust mechanical stability | Cost-effective, versatile |

| BT Resin | High glass transition temperature (>170°C) | High reliability | Improved signal integrity, ideal for high-performance |

| Ceramic | High thermal conductivity, excellent insulation | Mechanical robustness | Durable, suitable for harsh environments |

| Polyimide | High thermal stability (up to 300°C) | Flexibility | Lightweight, chemical resistance |

You should avoid common mistakes in material selection. Ignoring compatibility between substrate materials can lead to warpage and solder joint failures. Neglecting pad finish requirements or cleanliness standards increases the risk of assembly defects and latent shorts.

| Mistake | Description | Impact |

|---|---|---|

| Ignoring Material Compatibility | Choosing incompatible materials | Increases warpage-related failures by up to 12% |

| Neglecting Pad Finish | Selecting finishes based only on cost | Can cause up to 9% of assembly defects |

| Failing Cleanliness Standards | Not enforcing cleanliness | Raises risk of latent shorts in humid environments |

Tip: Always match substrate materials for compatibility and specify cleanliness standards in your designs to prevent reliability issues.

Thermal Management Tips

Effective thermal management is essential for every semiconductor packaging substrate. You must consider both material properties and cooling solutions to maintain optimal device temperatures. Advanced packaging methods often use novel thermal interface materials, such as phase change materials, liquid metal alloys, and graphene, to improve heat dissipation. You can also implement heat spreaders, heat sinks, vapor chambers, and direct liquid cooling for high-performance designs.

| Strategy Type | Description |

|---|---|

| Novel Thermal Interface Materials | Use phase change materials, liquid metal alloys, and graphene for high thermal conductivity |

| Cooling Solutions | Apply heat spreaders, heat sinks, heat pipes, vapor chambers, and direct liquid cooling |

| Thermal Test Vehicles | Use thermal test chips to simulate real chip conditions and validate thermal performance |

Ceramic substrates, especially aluminum nitride, offer high thermal conductivity and efficient heat dissipation. Aluminum substrates provide even higher thermal conductivity, making them suitable for power electronics and LED lighting.

| Substrate Material | Thermal Conductivity (W/m·K) | Heat Dissipation Efficiency | Applications |

|---|---|---|---|

| Aluminum | 200 to 250 | High | LED lighting, power electronics |

| Ceramic | 20 to 200 | Moderate to High | High-performance applications |

Note: You should always validate your thermal management designs using simulation tools and thermal test vehicles to ensure reliability under real-world conditions.

Mechanical Stability Factors

Mechanical stability is critical for preventing warpage, cracking, and delamination in semiconductor packaging substrate designs. You must address the mismatch in coefficients of thermal expansion (CTE) between different materials. Warpage often occurs in 2.5D ICs when materials expand and contract at different rates during temperature changes. Low warpage materials help prevent stress accumulation and maintain structural integrity.

- Match the CTE of molding compounds with silicon to reduce thermal stress.

- Use low warpage materials to ensure long-term reliability.

- Model mechanical stress during thermal cycles to prevent delamination and cracking.

Package substrates provide mechanical support and protection for IC components. They distribute mechanical stresses and vibrations, reducing the risk of damage during handling, assembly, and operation. You should always include stress modeling in your designs to maintain reliability throughout the product lifecycle.

Tip: Collaborate with material suppliers and use simulation tools to optimize mechanical stability in your semiconductor packaging substrate designs.

Semiconductor Packaging Techniques & Best Practices

Signal Integrity Methods

You must prioritize signal integrity when designing semiconductor packaging techniques. Signal quality directly impacts device performance, especially in high-speed applications. You can minimize crosstalk and electromagnetic interference by placing electromagnetic shields between circuit layers and using grounded planes. Sandwiching signal traces between solid ground or power planes creates stable return paths and effective shielding. Increasing the distance between traces lessens coupling and enhances signal integrity. Using lower dielectric constant materials in high-density substrates reduces crosstalk by up to 50 percent, which improves overall performance.

| Method | Description |

|---|---|

| Signal layer placement | Sandwich signal traces between solid ground or power planes for stable return paths and shielding. |

| Ground and power planes | Use continuous planes close to signal layers for better shielding and reduced crosstalk. |

| Trace spacing | Increase distance between traces to lessen coupling and enhance signal integrity. |

| Solid ground planes | Ensure ground planes are solid to minimize noise coupling and provide low-impedance return paths. |

| Shielding with planes | Use ground planes between signal layers to block noise and prevent signal radiation. |

| Minimizing layer-to-layer coupling | Position signal layers close to ground or power planes for effective shielding against EMI. |

Advanced semiconductor packaging techniques reduce signal attenuation and crosstalk, leading to higher data transmission speeds. High-end substrates minimize signal loss and preserve integrity, supporting precise signal timing at high frequencies.

Power Delivery Optimization

You need to optimize power delivery networks in semiconductor packaging techniques to minimize voltage drop and power noise. Proper grounding techniques, such as star grounding or ground planes, reduce voltage drop impacts. Impedance matching ensures the output impedance matches the transmission line impedance, which preserves signal quality. You should use time-domain reflectometers to identify and address potential signal integrity issues due to voltage drops. Optimizing the layout with decoupling capacitors and power rails stabilizes voltage levels across the system. Shielding and routing techniques protect signals from external noise and mitigate voltage drop effects. Incorporating sufficient noise margins ensures signal integrity under varying voltage conditions. Implementing heat management techniques regulates temperatures and prevents signal degradation.

| Aspect | Traditional Packaging | Advanced Packaging |

|---|---|---|

| Power Delivery Network Design | Frontside network of low-resistive metal wires | Backside power delivery network |

| IR Drop | Higher due to shared space with signal network | Reduced by decoupling from signal network |

| Routing Congestion | Increased due to competition for space | Decreased with wider, less resistive lines |

| Standard Cell Height Scaling | Limited by power and ground rails | Enhanced by buried power rails and nTSVs |

| Power Density | Challenges in maintaining margins | Improved performance with direct delivery |

Controlled Impedance Routing

Controlled impedance routing is essential in semiconductor packaging techniques for maintaining signal quality and device performance. You should avoid splitting ground planes under high-speed traces to prevent longer, noisier return paths. Route high-speed traces over a continuous reference plane and use stitching capacitors or ground vias if crossing a plane split. Balanced return paths for differential pairs help avoid common-mode noise. Use 45-degree angles or smooth curves for routing to minimize impedance discontinuities. Match trace lengths in differential pairs to prevent skew and data errors.

- Ensure trace geometry is within manufacturer’s tolerance, typically ±5 mil for high-speed designs.

- Route differential pairs symmetrically and keep signals parallel.

- Maintain uniform clearance between traces along their entire length.

- Route both traces on the same layer whenever possible to avoid impedance variation.

- Keep differential impedance tightly controlled, typically 90 Ω ± 10%.

Controlled impedance routing prevents signal distortion by matching trace impedances. This ensures accurate and efficient signal transmission, which is crucial for high-speed applications. Maintaining signal fidelity requires a detailed understanding of impedance control. You must use impedance calculators, signal integrity analysis, and design rule checks to enforce trace spacing and width constraints. Research from the semiconductor industry confirms that proper impedance matching minimizes signal degradation and maintains integrity, especially in advanced semiconductor packaging techniques.

Challenges & Solutions in Packaging Substrate Design

High-Density Interconnect Issues

You face significant challenges when designing high-density interconnects for semiconductor devices. The complexity of wafer-level packaging and advanced interconnects increases the risk of design errors and performance bottlenecks. The table below highlights common issues you encounter in high-density interconnects:

| Issue Type | Description |

|---|---|

| Via Size | BGA components determine the required via size, impacting design precision. |

| Routing Considerations | Changes in routing due to microvia aspect ratios can affect substrate thickness and impedance. |

| Signal Integrity (SI) | Dense routing can lead to crosstalk and other SI issues, necessitating careful design considerations. |

| Material Selection | Choosing appropriate materials is critical to avoid fabrication issues and ensure performance. |

To overcome these challenges, you can use several proven strategies:

- Attach heat sinks and integrate active cooling to lower temperatures.

- Employ vapor chambers and heat pipes for superior thermal conductivity.

- Replace standard materials with insulated metal substrate PCBs for better thermal performance.

- Integrate liquid cooling for extreme power densities in advanced semiconductor devices.

A recent case study in the USA showed that separating circuits into rigid PCBs and flexible circuits reduced costs by over 40% for a battery management solution, while maintaining robust performance.

Warpage and Reliability

Warpage remains a critical concern in semiconductor packaging. You must address material-induced warpage, process-induced warpage, and design-induced warpage to ensure reliability. Variations in the coefficient of thermal expansion among materials often cause warpage, especially in wafer-level packaging. Inconsistent fabrication processes and unbalanced substrate architecture also contribute to reliability failures.

Reliability challenges are also in focus. Thinner dies improve performance but make chips more fragile, increasing risks such as warpage, die-pop, and electromigration. Optimized reflow processes are helping to reduce these defects and improve long-term reliability.

Advanced packaging involves increasingly challenging requirements for heterogeneous integration and chiplet packaging. Needs such as fine pitch interconnects, finer lines/spaces, and more distribution layers require intensive engineering design to minimize warpage and maximize thermal performance while retaining reliability in harsh conditions.

You should model mechanical stress and optimize reflow processes to reduce warpage and improve the reliability of semiconductor devices.

Supplier Collaboration

You need strong supplier collaboration to achieve success in semiconductor packaging substrate projects. Effective communication, technical support, and after-sales service play vital roles. Material quality and technological expertise from suppliers ensure that your semiconductor devices meet performance standards. Supply chain stability and cost competitiveness also impact your project outcomes.

Key partners include EDA vendors, substrate suppliers, equipment vendors, chiplet designers, system houses, OSATs, and educational institutions. Early supplier involvement leads to improved design efficiency and reduced costs. Regular review meetings and joint development agreements foster innovation and enhance product quality.

| Evidence | Description |

|---|---|

| Supplier Involvement | Early supplier involvement leads to improved design efficiency and reduced costs. |

| Financial Returns | Supplier integration can produce significant improvements in financial returns and product design performance. |

| Coordination | ESI acts as a coordinating mechanism linking product, process, and supply chain design. |

You should integrate suppliers early in the development process to capture cost-saving ideas and prevent costly delays in semiconductor projects.

Next Generation IC Packaging Trends

Silicon Scaling & Functional Density

You see rapid changes in next generation ic packaging as silicon scaling pushes the boundaries of semiconductor design. Advanced packaging technologies now support larger, more densely packed chips. You benefit from innovations like through-silicon via technology, which boosts information transmission speed for high bandwidth memory. Chiplet technology also gains momentum, letting you integrate multiple smaller chips to improve yields and specifications. These innovations increase functional density and enable new levels of device performance.

- Advanced packaging accommodates larger, denser chips.

- Through-silicon via technology enhances memory bandwidth.

- Chiplet integration improves manufacturing yields and device specifications.

You face new substrate design challenges as silicon scaling advances. The table below outlines key issues:

| Challenge | Description |

|---|---|

| Thinner semiconductor channels | You must select substrate materials and deposition techniques to support thinner channels. |

| 2D material integration | Integrating 2D materials complicates gate stack and dielectric deposition. |

| Deposition of 2D materials | You can use direct growth or transfer methods for 2D material layers. |

| Gate stack and dielectric deposition | Weak van der Waals forces in 2D materials challenge traditional deposition techniques. |

Heterogeneous Integration

Next generation ic packaging relies on heterogeneous integration to combine optimized components in a single package. You see substrates evolving from simple carriers to complex system integration platforms. SIP architectures grow more complex and diverse, supporting a wide range of semiconductor applications. Interconnection techniques shift from via-centric to via-less designs and from micro-bumps to hybrid bonding. Multi-die advanced packages integrate high-performance logic and memory, reducing latency and power consumption.

| Approach | Description |

|---|---|

| Evolution of Substrates | Substrates now serve as system integration platforms. |

| Architecture Complexity | SIP architectures support diverse semiconductor applications. |

| Interconnection Techniques | Hybrid bonding and via-less designs improve performance. |

| Multi-die Advanced Packages | Integration of logic and memory reduces latency and power use. |

| Complex System Integration (CIS) | You address challenges from design to test with advanced integration. |

You gain several advantages from heterogeneous integration:

- Reduced signal propagation delays

- Enhanced memory bandwidth

- Improved system latency

- Higher operating frequencies

- Miniaturization with high performance and energy efficiency

- Stacking memory dies above processing units for faster access

These innovations support high-performance computing in AI and 5G systems.

Ceramic Package Applications

Ceramic substrates play a vital role in next generation ic packaging for semiconductor devices. You benefit from enhanced thermal management, improved solderability, and moisture resistance. Ceramic packages offer efficient heat dissipation and superior electrical performance, making them ideal for high-power and high-frequency applications. However, you must address soldering difficulties, repair challenges, and reliability issues during thermal cycling.

| Advantages | Limitations |

|---|---|

| Enhanced thermal management | Soldering difficulties |

| Improved solderability | Repair challenges |

| Repairability | Reliability issues in thermal cycling |

| Moisture resistance | Moisture sensitivity |

You compare ceramic substrates to organic substrates for thermal and electrical performance:

| Property | Ceramic Substrates | Organic Substrates (e.g., FR-4) |

|---|---|---|

| Thermal Conductivity | Superior, ideal for high-power applications | Lower, suitable for general-purpose use |

| Heat Dissipation | Efficient, prevents thermal buildup | Limited, not ideal for high-power applications |

| Electrical Performance | Better for high-frequency applications | Less effective, higher signal attenuation |

You see ongoing innovations in ceramic package applications, supporting the demands of next generation ic packaging and advanced semiconductor systems.

Essential Tools & Resources

Design Software

You need reliable design tools to create advanced semiconductor packaging substrates. Industry leaders rely on multiphysics modeling and simulation to achieve precision in every stage of development. Siemens provides a comprehensive design and verification solution that covers everything from prototyping to final implementation. This approach helps you meet performance targets, especially as silicon scaling becomes more demanding. Many engineers now use cloud-based design tools to handle the complexity of miniaturized semiconductor components. These platforms support high-resolution meshes, which are essential for capturing the fine details in next-generation design and verification solution workflows. Automated verification of heterogeneous assemblies ensures that your designs remain robust as you integrate more diverse components.

Simulation Tools

Simulation tools play a vital role in semiconductor substrate design. You can use Ansys Sherlock to track mechanical fatigue and stress throughout a PCB’s lifecycle. This tool predicts potential failures and helps you optimize your designs before production. The Ansys ecosystem supports realistic modeling of electrical circuits, thermal performance, and mechanical strength. Icepak allows you to evaluate cooling solutions and dynamic thermal management, making sure your semiconductor designs stay within safe temperature limits. Multi-field coupling analysis on TSV structures helps you identify and address reliability issues early in the process. These simulation tools form the backbone of any effective design and verification solution.

- Track mechanical fatigue and stress with advanced simulation tools.

- Evaluate cooling and thermal management strategies.

- Optimize reliability with multi-field analysis.

Tip: Use simulation tools early in your workflow to reduce costly design changes later.

Industry Standards

You must follow industry standards to ensure your semiconductor packaging substrates meet global requirements. Compliance leads to safer products, smoother regulatory approval, and greater market acceptance. Certification also sets you apart from competitors and builds trust with clients.

| Advantage | Explanation |

|---|---|

| Enhanced Product Safety | Consistent quality reduces the risk of defects or contamination. |

| Regulatory Confidence | Compliance with international standards facilitates approval processes in global markets. |

| Operational Efficiency | Optimized workflows enhance productivity and minimize waste. |

| Market Competitiveness | Certification establishes trust with clients and sets manufacturers apart from competitors. |

You should always integrate industry standards into your design and verification solution to streamline workflows and improve product reliability. Staying updated with evolving standards ensures your semiconductor products remain competitive in a fast-changing market.

Why Choose BSTCERAMIC

You want your semiconductor projects to succeed. BSTCERAMIC gives you a competitive edge in advanced packaging substrate design. You gain access to high-performance ceramic substrates that meet the demands of next-generation semiconductor devices. Industry research, such as the IEEE Transactions on Components, Packaging and Manufacturing Technology, shows that ceramic substrates deliver superior thermal management and reliability for semiconductor applications.

You benefit from BSTCERAMIC’s commitment to quality and innovation. The company invests in research and development to stay ahead of semiconductor industry trends. You receive technical support from experts who understand the challenges of substrate design. BSTCERAMIC partners with leading semiconductor manufacturers to deliver solutions that meet strict performance standards.

Tip: You can request custom substrate designs to match your unique semiconductor requirements. BSTCERAMIC engineers work with you to optimize thermal conductivity, mechanical stability, and signal integrity.

Consider the advantages you get when you choose BSTCERAMIC:

| Feature | Benefit for Your Semiconductor Project |

|---|---|

| High Thermal Conductivity | Keeps semiconductor devices cool and reliable |

| Mechanical Robustness | Prevents warpage and cracking |

| Precise Manufacturing | Ensures consistent quality for every batch |

| Expert Collaboration | Solves complex semiconductor design issues |

| Fast Prototyping | Speeds up your development cycle |

You improve your semiconductor device performance with BSTCERAMIC’s advanced materials. You reduce the risk of reliability failures and achieve better results in high-power and high-frequency applications. You also gain peace of mind knowing your substrates meet international standards and pass rigorous testing.

You can contact BSTCERAMIC for a consultation or sample request. The team responds quickly and helps you select the best substrate for your semiconductor project.

You now have a checklist for advanced semiconductor packaging substrate design.

- Select materials with proven thermal and mechanical stability.

- Validate thermal management using simulation tools.

- Collaborate with suppliers for reliable results.

For deeper insights, review IEEE Transactions on Components, Packaging and Manufacturing Technology. Stay updated with industry trends to improve your next project.

HOME

HOME